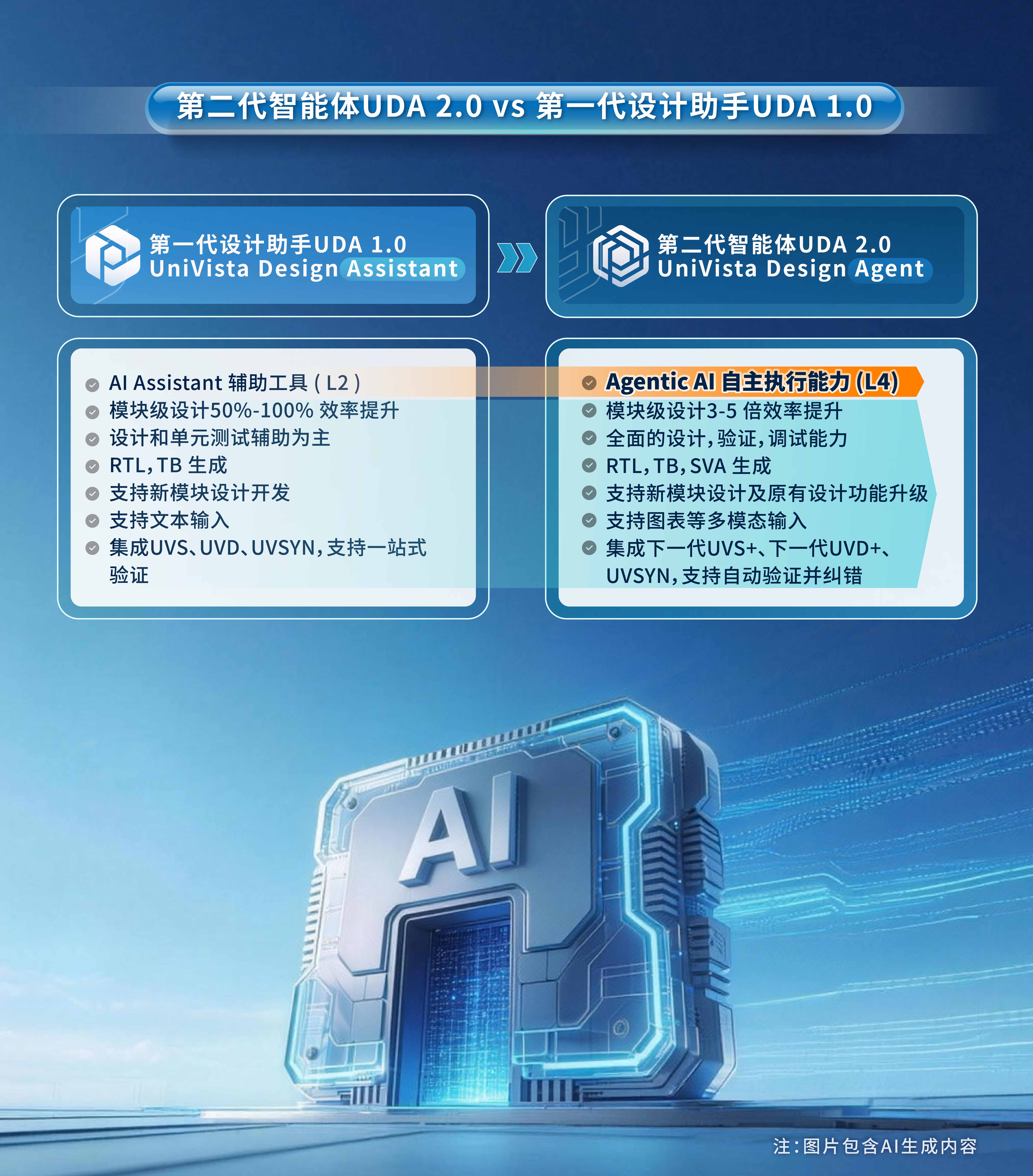

合见工软推出第二代数字设计AI智能平台——智能体UniVista Design Agent (UDA) 2.0。此次升级后,UDA平台正式从智能辅助工具进化为真正意义上的Agentic AI智能体。UDA 2.0是国内首款基于全部自主研发EDA架构上的领先智能体EDA工具,它能够在接受工程人员设计需求和指导后自主完成RTL设计、验证、纠错与优化全流程任务,标志着国产EDA自主式智能体的时代全面开启。合见工软始终致力于大幅提升数字芯片设计效率,为中国集成电路产业应对高复杂度与快速迭代挑战提供核心生产力引擎。

智能体UDA 2.0 基于业界DeepSeek等先进大模型,内嵌多个针对数字电路设计的逻辑综合、性能评估、功能分析和验证等专业EDA引擎,不再仅仅是一个响应指令的工具,而是一个能够自主规划与执行任务的智能体。它能够理解自然语言描述的设计意图,自动调用底层引擎,完成从RTL代码生成、代码检查、验证调试并持续迭代优化的完整闭环,从而赋能设计师聚焦于硬件算法和架构设计等更高价值的创造性工作,进一步提升设计质量和生产力。

(本页面所述产品效率、性能提升数据均基于合见工软实验室特定测试场景及用户调查,实际使用效果因用户的设计需求、应用环境等因素存在差异,仅供参考)

产品特性

- 支持基于Agentic AI自主规划并执行任务,覆盖从RTL生成、优化、验证到调试的全流程。模块级设计验证效率提升 3-5 倍

- 支持基于自然语言的指令或Spec,自动生成高质量Verilog RTL代码,并支持语法和设计规范检查及自动纠错

- 支持基于已有RTL 代码开发新功能,并支持含图表,波形图的多模态Spec

- 支持设计空间探索及用快速综合工具RTL_Eval 做设计QoR快速预估。并可通过多轮迭代,自主进行代码时序面积优化,可提升代码性能10-20%

- 支持自动生成TestBench和SVA断言,支持UVM框架

- 支持基于内嵌的仿真工具UVS+与调试工具UVD+,自动分析问题并纠错

- 支持自动生成代码解释和代码注释

- 支持多任务并发,成倍提升效率

- 支持挂接企业知识库,进行知识问答

- 支持企业私有环境部署,确保数据安全

- 全面的用户、任务、知识库等管理功能,并提供功能使用统计分析