上海合见工业软件集团股份有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)和IP领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

EDA是集成电路设计工业软件,应用于芯片的设计、制造、封测等多个环节,承担着电路设计、电路验证和性能分析等多项芯片开发过程中的核心工作,IP作为已验证且可重复利用功能模块,是现代超大规模集成电路设计的基石。在地缘政治格局剧烈变化的时代,EDA与IP是中国科技自主化进程中的关键一战,是国家战略层级的核心问题之一。中国EDA需要尽快赶超国际领先水平,从而打造新一代的世界级工业软件。

在这样的产业发展背景下,合见工软应运而生,以自主自研的创新EDA产品推动产业成就客户。合见工软于2020年成立,公司的发展与自主研发实力多次获得认可与支持,现已荣获国家级专精特新“小巨人”企业、国家级高新技术企业等认定,产品获得中国集成电路创新联盟“IC创新奖”、“中国芯”优秀支撑服务产品等多项荣誉资质。公司始终坚持自主创新发展,截至2026年3月31日已累计获得各类有效知识产权300 余项,包括发明专利、实用新型专利及软件著作权等,持续夯实技术护城河。

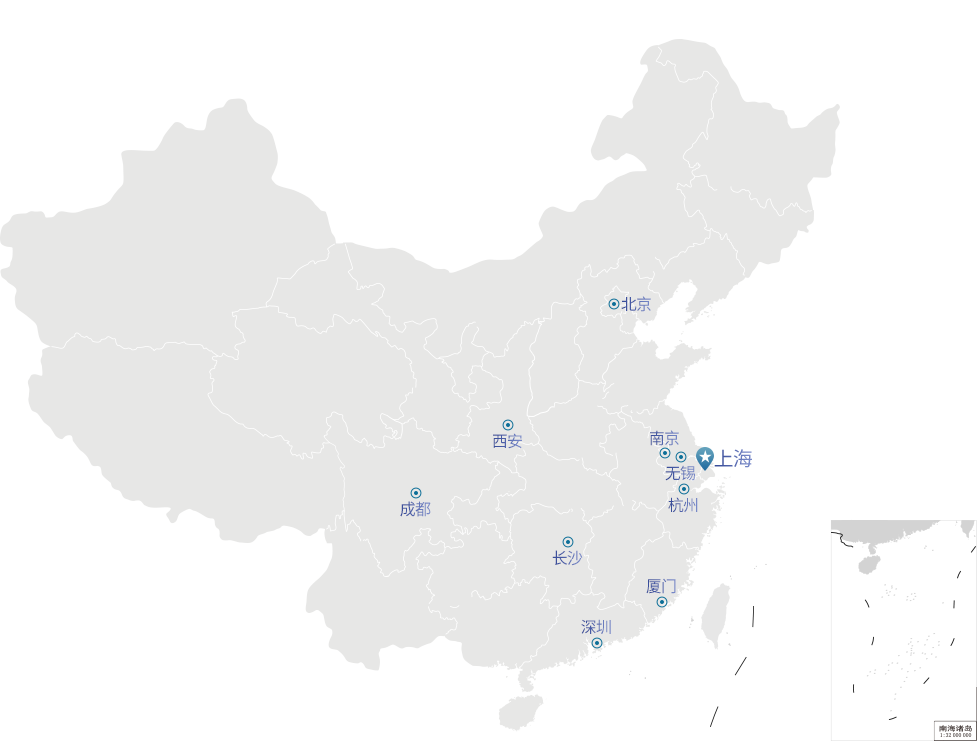

合见工软总部位于上海,创始团队来自国际领先的EDA公司,多位核心领导都曾担任这些公司的全球副总裁及最高技术职位 (Fellow),集团员工约1300人,国际EDA专家数量在国内同领域企业中占据优势。在合见工软创新团队中,众多人员拥有15至20年EDA领域从业经验,具备深厚的技术背景和高超的专业能力。

合见工软产品线已覆盖数字芯片EDA工具、系统级工具及高速接口IP,是国内唯一一家可以完整覆盖数字芯片验证全流程,DFT可测性设计全流程,并同时提供先进工艺高速互联IP的国产EDA公司。自成立以来,合见工软一直以国际先进水平为目标,多产品线并行研发,为中国半导体企业提供了芯片硅前和硅后的高性能EDA工具和IP解决方案。

合见工软以五年40余款产品的创新速度、硬核的技术实力,引领了中国EDA企业发展与生态建设的新态势。其产品部分性能已达国际标杆水平,获得国内众多IC企业的广泛认可及规模化部署,核心产品市场占有率稳居行业前列。目前,合见工软的客户及合作伙伴已覆盖智算超算、通信网络、消费电子等领域的主流企业。

秉承“联结数字和物理世界,成就创意到产品实现”的愿景,合见工软将始终坚持自主研发,开拓创新,建设生态,目标打造全国产芯片设计全流程解决方案,并提供世界一流水平的EDA产品,推动芯片产业高质量发展。心怀“因应时代变局,致力创新突破,打造世界级EDA产品,成就客户推动产业”的使命,合见工软将支撑起中国集成电路自主研发的重担,凭借深刻的产业理解力、先进的EDA及综合技术能力、对客户痛点的深刻理解力,以创新的技术和应用模式服务中国及全球客户,携手业界同仁,共同创造中国芯片产业卓尔不凡的美好未来。

目前合见工软的全系列产品线包括:

全国产自主自研数字芯片验证全流程解决方案:全面覆盖从早期虚拟架构设计建模、中期硬件仿真加速、中期子系统级软件到后期全芯片级原型验证的全场景需求,具体产品包括:

- 下一代全功能高性能仿真器 UniVista Simulator Plus (UVS+),下一代全功能高效能数字验证调试平台 UniVista Debugger Plus (UVD+),验证效率管理系统 UniVista Verification Productivity System (VPS):验证软件工具实现数字功能仿真签核,打造全国产一站式验证流程,全自研架构,并支持国产服务器生态

- 全场景验证硬件系统UniVista Unified Verification Hardware System(UVHS/UVHS-2):最新发布的UVHS-2最大可级联高达192片AMD最新型号FPGA芯片

- 数据中心级全场景超大容量硬件仿真加速验证平台UniVista Hyperscale Emulator(UVHP):国产自研硬件仿真器中首台可扩展至460亿逻辑门设计的产品

- 单系统先进原型验证平台PHINE DESIGN Advanced Solo Prototyping(PD-AS):搭载单颗AMD最新型号FPGA芯片

- 虚拟原型设计与仿真工具套件UniVista V-Builder/vSpace:构筑“芯片+软件+系统+应用”电子系统与芯片设计联动平台

国产自主知识产权的可测性设计(DFT)全流程平台UniVista Tespert,该平台集成了一系列高效工具,包括边界扫描测试软件工具UniVista Tespert BSCAN、存储单元内建自测试软件工具UniVista Tespert MBIST、测试向量自动生成工具UniVista Tespert ATPG、缺陷诊断软件工具UniVista Tespert DIAG、良率分析工具UniVista Tespert YIELD。目前UniVista Tespert系列已经实现了在汽车电子、高阶工艺芯片等领域的国内头部IC企业中的成功部署,应用于超过50多个不同类型芯片测试,是合见工软更广泛的数字实现EDA产品组合的重要产品之一。

国内首款Agentic AI自研EDA平台:最新发布的第二代数字设计AI智能平台——智能体UniVista Design Agent (UDA) 2.0,是国内首款基于全部自主研发EDA架构的领先智能体EDA工具,它能够在接受工程人员设计需求和指导后自主完成RTL设计、验证、纠错与优化全流程任务,标志着国产EDA自主式智能体的时代全面开启。智能体UDA 2.0已经从“Level 2:对话式 LLM 辅助工具”,演进到“Level 4:Agent 工作流 - 自主设计者”,深度融合了大模型(LLM)与合见工软自研的EDA工具链(包含UVS+软件仿真、UVD+软件调试、UVSYN逻辑综合等),并将芯片设计行业知识深度融入Agentic AI系统中,实现了芯片设计从自然语言描述到高质量代码产出的一站式自动化。

合见工软可提供的广泛IP解决方案包括:

- 全国产接口IP方案:UniVista PCIe Gen5完整解决方案,以太网(Ethernet)、灵活以太网(FlexE)、Interlaken等多种高速互联接口控制器,Memory接口HBM3/E、DDR5、LPDDR5 IP,先进工艺多协议兼容、集成化传输接口SerDes IP解决方案UniVista 32G Multi-Protocol SerDes IP;

- 智算组网类IP方案:Scale-out应用解决方案UniVista RDMA IP,Scale-up应用解决方案UniVista PAXI IP,推动智算互联的超以太网IP解决方案UniVista UEC MAC IP;

- 针对先进封装芯粒(Chiplet)集成的标准IP方案:国产HiPi标准IP/VIP,Chiplet国际关键标准UCIe IP,同时为了突破算力限制,合见工软提供了UCIe跨工艺互连D2D和C2C两种应用,实现了国产首个跨工艺节点的UCIe IP互连技术验证。

合见工软的高速接口IP解决方案支持多家先进工艺,已经流片验证,并已在国内领先IC企业芯片中成功部署,引领智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。

合见工软覆盖“元器件库+数据管理+流程管理+设计工具”的系统级EDA全流程解决方案包括:在PCB板级,合见工软推出了创新电子系统设计平台UniVista Archer,其包含一体化PCB设计环境UniVista Archer PCB和板级系统电路原理设计输入环境UniVista Archer Schematic,组成了完整的复杂电子系统设计及PCB板级设计解决方案,解决了高速、多层PCB设计中带来的设计与仿真挑战,带来更高的性能与可靠性,现已实现在人工智能、云计算、通信、智能汽车、智能手机等领域的国内头部企业中的成功部署应用。在封装和系统级,合见工软提供了先进封装的协同设计平台UniVista Integrator,可高效解决2.5D、3D、SIP等各种先进封装设计需求的协同设计;以及新一代电子系统研发管理环境UniVista EDMPro,组成了完整的一站式电子设计数据管理平台及应用解决方案,现已实现在消费电子、通讯、计算机、航天航空等领域的国内头部企业中的成功部署应用。

合见工软深度适配的垂直行业解决方案包括:

面向智算芯片的一站式解决方案:

- 在智算芯片领域,合见工软推出支持智算超节点互联硅前验证的芯片开发一站式解决方案,整合数字EDA全流程工具、高速接口IP、系统级验证平台及专业服务,覆盖从IP选型、架构设计、组网验证、良率提升到封装优化的全过程,帮助客户系统性应对算力、存储、互联与能效挑战。

RISC-V全栈验证与测试解决方案:

- 合见工软RISC-V全栈验证与测试解决方案,通过提供数字仿真全流程工具平台、原型验证与硬件仿真全系列产品集、虚拟原型与硬件混合仿真套件、可测性设计全流程解决方案,从架构定义到芯片实现全面革新RISC-V质量新范式, 为RISC-V芯片的大规模可靠商用铺平道路。

Chiplet芯片设计IP+EDA集成解决方案:

- 合见工软面向Chiplet芯片设计的IP+EDA集成解决方案,涵盖Chiplet EDA和设计方法学、Chiplet接口和子系统解决方案、Chiplet IP、NoC+UCIe整体方案、Chiplet inner die/ die-to-die验证方案以及先进封装设计与SI/PI能力。该方案连接先进晶圆厂与OSAT,帮助客户完成算力分配的性能分析、封装选型与整体PPA评估,为Chiplet芯片和系统设计提供完整支撑。