了解更多信息,请联系:

7月16日-19日,第五届RISC-V中国峰会在上海张江科学会堂成功举办。峰会期间,中国数字EDA/IP龙头企业上海合见工业软件集团有限公司(简称“合见工软”)携手合作伙伴开芯院进行联合演讲,用实际案例诠释了EDA工具如何破局高性能RISC-V多核芯片验证效率的痛点,让大家看到国产EDA在推动RISC-V产业落地、协同创新方面的硬核突破与生态活力。

赋能“香山”高性能开源RISC-V处理器大型系统构建

在峰会期间举办的“EDA分论坛”上,合见工软验证产品市场总监曹梦侠与北京开源芯片研究院高级工程师李贤飞,共同做题为《面向高性能RISC-V多核处理器的硬件验证方法学-香山昆明湖16核完整系统的大级联FPGA系统验证实践》的报告。

▲北京开源芯片研究院高级工程师 李贤飞

▲合见工软验证产品市场总监 曹梦侠

昆明湖是“香山”系列处理器的第三代架构,面向服务器、数据中心等高性能计算场景设计,支持64核,性能对标ARM Neoverse N2。通过全球首个开源大规模片上互联网络(NoC)IP温榆河,支持12*12网格最大支持256个处理器互联。李贤飞指出,昆明湖多核CPU架构对于验证提出多方面挑战:

- 一是规模大:多核CPU系统包含复杂的总线、多级缓存和DDR4、UART等接口 ,逻辑规模远超单片FPGA容量。传统FPGA平台资源不足,且手动分割设计的方式困难且极易出错,Porting周期极长。

- 二是性能要求高:目标是在FPGA上实现足够高的运行速度(最终目标10MHz),从而运行操作系统并进行有意义的软硬件协同验证。

- 三是调试困难:需要保障16核缓存一致性、总线完整及高负载下调度优化。同时,需要快速定位和复现因跨核交互、缓存一致性等引起的深层次Bug。缺乏专用调试工具,问题定位慢。

“与合见工软合作之前,香山系列多核CPU验证亟须大规模FPGA平台与自动化工具链。”李贤飞说。正是在这样的挑战之下,促成与合见工软展开合作。继双方2024年“香山”第二代南湖架构验证项目后的技术成果发布之后,如今第三代昆明湖架构合作成果的发布标志着双方携手探索大型处理器验证技术突破的再次升级。

据曹梦侠介绍,在“香山”第二代“南湖”及第三代“昆明湖”处理器开发和软件生态系统优化中,成功应用了合见工软的全场景验证硬件系统UniVista Unified Verification Hardware System(简称“UVHS”),显著提升了开发效率。

合见工软UVHS硬件验证平台的优势体现在如下方面:

- 高性能与大容量:UVHS作为一款商用级全场景验证硬件系统,具备高性能和大容量的特点,能够满足大规模ASIC/SOC软硬件验证的需求。

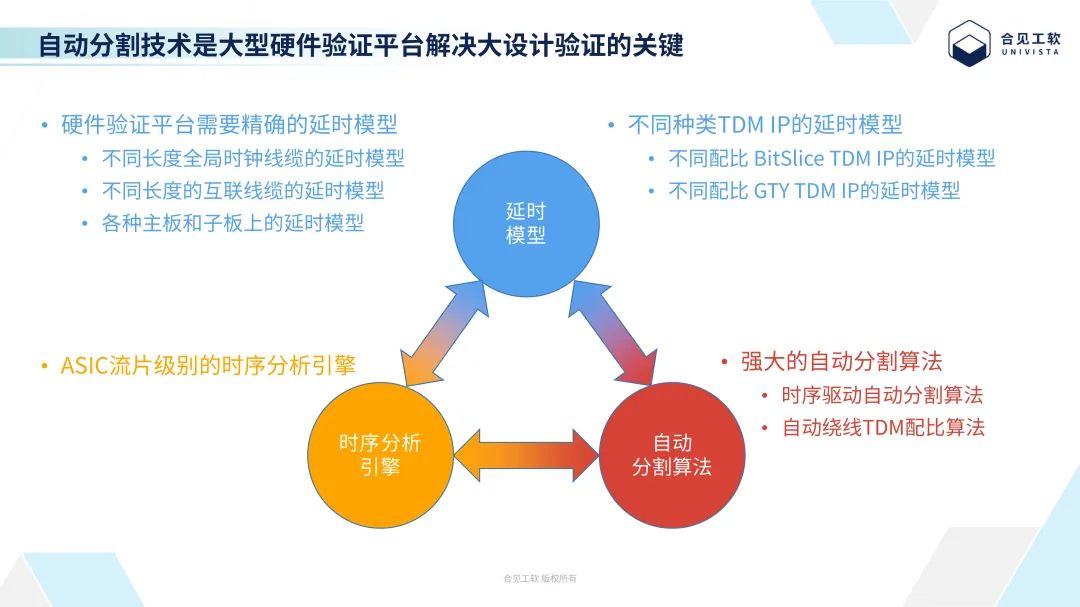

- 智能化自动分割技术:该技术可将大型系统快速编译移植,将多核设计分割到多片FPGA上,自动化程度高,简化了工程师的手动工作,提高了验证效率。

- 自动化的代码移植和编译全流程:最大化减少用户从ASIC代码移植到FPGA工程的人力成本,提供从RTL到Bitfile的自动化流程。

- 高运行性能:基于Xilinx新型FPGA平台,UVHS的全局时序驱动智能自动分割技术可显著提升运行性能,缩短软件运行时间,优化软件开发项目周期。

- 大规模系统级联能力:支持大系统级联,最多可级联上百亿逻辑门规模,已成功部署实现最大160片FPGA的级联,为RISC-V大型系统扩展提供可靠技术支撑。

- 丰富的接口和存储模型:提供PCIe Gen5、MIPI CSI2/DSI2、Ethernet 1G-800G等多种高速接口,以及DDR5、DDR4、LPDDR5、LPDDR4、HBM3等存储模型,帮助用户快速搭建完整验证场景。

- 强大的调试功能:支持UHD无限深度波形调试、触发、异步寄存器读回等功能,类似仿真方式的波形调试功能,显著提高调试效率和问题定位能力。

其中,UVHS Compiler的智能化自动分割技术发挥了关键作用。

“香山”处理器的灵活扩展性需要将大的多核设计能够分割到多片FPGA上。UVHS Compiler的智能自动分割技术将整个过程完全自动化,同时其强大的时钟转换引擎可自动处理设计内多路异步时钟,大幅简化了工程师的手动工作,更容易将为ASIC设计的RISC-V RTL代码快速迁移到FPGA平台,“香山”的双核RTL代码导入时仅用不到一周时间即实现了UVHS上的Linux OS启动。

基于昆明湖多核CPU验证项目的经验总结,合见工软提出了“四步走”的系统化多核处理器 FPGA验证方法论,涵盖从设计移植到系统调试的完整流程,为RISC-V多核验证提供了标准化路径:

- 1-设计移植与适配 (Porting): 建立了ASIC-to-FPGA的自动化适配流程,包括时钟树、存储模型、接口IP转换的标准化处理方法。

- 2-编译迭代效率与资源优化使用的最大化平衡:向大规模设计,在资源占用率与高效率编译迭代之间动态取舍,寻找最大化的收益平衡点。

- 3-渐进式启动策略 (Bring-up): 创新提出了核数逐步扩展的验证策略,结合单核到多核的系统复杂度梯度,有效降低了系统调试难度。

- 4-软硬协同调试技术 (Debug): 基于硬件仿真与后门加载技术的协同调试方案,精准解决系统启动故障,并实现内核加载速度量级突破。

在合见工软UVHS硬件平台的强大助力下,该项目产生三方面成果:

- 一是实现多版本全自动化编译流程:在项目初期移植阶段做完基础的移植工作后,后续的编译流程由UVHS工具自动化完成,包括时钟转换、自动分割、TDM IP绑定等关键工作。后续设计进版迭代,复用前套的自动化流程,省掉很多额外工作。

- 二是性能目标全面达成:

-

- 单核/双核/4核/8核版本CPU主时钟均能稳定运行在15MHz,为针对不同应用场景的性能评估和软件开发提供了高速验证平台。

- 16核完整版本CPU主时钟稳定运行在10.2MHz,超越原定10MHz目标。

- 项目首次在FPGA原型验证平台上,完整运行一个未经裁剪的、可启动OS的16核高性能昆明湖RISC-V处理器系统。

- 相比传统方法,整体验证效率提升约40%,大幅缩短产品上市时间。

- 三是构建一套灵活的多用户验证环境:项目开发了兼容16核DB和多个4核DB的boardfile,使验证平台能够灵活切换配置;验证平台可以被灵活划分为多个独立的4核系统,供4个不同软件或算法团队同时并行使用,大大提高了开发效率;一套硬件既能用于16核的系统级攻关,也能用于多团队的日常开发,大幅提升了硬件资源的利用率。

不仅如此,合见工软新技术-自研FPGA综合器UVSyn,对比FPGA自带综合器实现了多项指标提升,带来了资源优化、性能提升、编译效率提升。

- 资源优化:LUT总量从4840万降低到4264万,节省11.9%关键资源,使设计布局更加灵活。

- 性能提升:时钟频率从8.8 MHz提升至10.2 MHz,增加15.0%,成功突破项目目标。

- 编译效率提升:编译时间从41小时缩短至35小时,效率提升14.6%。

对于双方后续项目工作展望,李贤飞表示,将在验证效能深化、更大规模设备扩展、更多核心场景验证等方面继续推进。后续温榆河片上网络与昆明湖架构的深度融合,将推动更大规模的32核至百核级众核系统的验证突破。同时,也希望EDA厂商开发更多支持CPU核心之外验证场景的特性,如UPF低功耗、DPA动态功耗验证等。此外,开芯院希望与EDA厂商协同推动RISC-V验证方法学标准化的工作,在工具链进化、生态建设等方面,促进产业链各方高效协作,加速 RISC-V产业的健康发展。

EDA协同推动RISC-V国产化落地加速

昆明湖16核处理器突破10.2MHz验证性能,展示了合见工软 UVHS全场景验证平台的实战成果,不仅为客户芯片研发提供了从 “设计构想” 到 “高效落地” 的硬核支撑,也勾勒出 RISC-V产业生态协同的创新范式。

未来,合见工软将始终将客户需求为先,通过自研创新,进一步提升芯片全场景验证的能力水平,通过与客户协同攻关,为客户提供匹配其产品定义和技术路线,更加高效、可靠的验证解决方案,助力客户实现验证效率瓶颈的突破,为RISC-V产业落地加速赋能。

关于合见工软

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,以EDA(电子设计自动化,Electronic Design Automation)领域为首先突破方向,致力于帮助半导体芯片企业解决在创新与发展过程中所面临的严峻挑战和关键问题,并成为他们值得信赖的合作伙伴。

了解更多详情,请访问www.univista-isg.com。